随着半导体技术向7nm及以下先进制程不断演进,芯片制造对精度的要求已迈入纳米级甚至亚纳米级门槛。化学机械抛光(CMP)作为目前唯一能实现晶圆表面全局平坦化的技术,其难度也随之呈指数级攀升。需要指出的是,半导体芯片的抛光包括了晶圆衬底抛光与IC集成电路抛光。与仅需处理单一材料表面平整的晶圆抛光不同,IC抛光面对的是芯片内部多介质、多结构的复杂场景,既要平衡不同材料的去除速率,又要兼顾全局与局部的完美共面性,技术门槛远高于晶圆抛光,已成为制约先进芯片量产的关键瓶颈之一。

从CMP的原理看,IC集成电路抛光的核心挑战

CMP抛光的本质是化学腐蚀与机械研磨的协同作用。其具体过程是,在一定压力下,将晶圆贴合于旋转的抛光垫上,同时在抛光垫与晶圆之间持续供给含有纳米磨料的抛光液。抛光液中的化学成分首先与晶圆表面材料发生化学反应,生成一层较软的表面改性层或氧化膜;随后,抛光液中悬浮的纳米磨料在机械作用下将这层改性层去除,露出新鲜的材料表面,化学反应得以继续。利用这种“化学-机械”的交替作用,CMP可以很好的兼顾避抛光效率与质量,成为现代芯片制造中不可或缺的全局平坦化技术。

然而,CMP技术在IC集成电路抛光中仍面临着复杂的现实挑战,一方面,IC抛光处理的并非均匀的单一材料,而是由氧化物、氮化物、金属、阻挡层等构成的异质多层结构,不同材料的物理化学性质差异巨大;另一方面,芯片表面的形貌也极不均匀:有高密度的细金属线阵列,也有孤立的宽金属线区域;有深宽比各异的沟槽结构,也有高低起伏的介质层堆积......这导致了IC抛光中最棘手的两类表面缺陷:蝶形下陷和侵蚀。

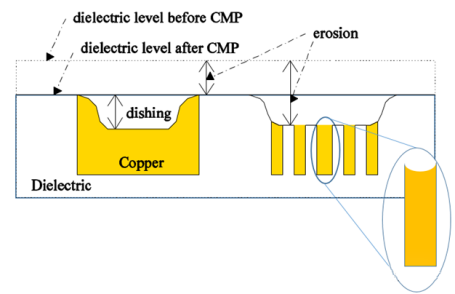

(1)蝶形下陷:通常出现在孤立或较宽的金属线区域。由于金属(如铜)的硬度低于周围的介质材料,在抛光过程中,机械作用更容易去除金属区域,导致金属线中心形成类似“碟形”的凹坑。蝶形下陷会显著降低互连线的有效截面积,增大电阻,恶化高频信号传输质量,并可能引发后续金属层覆盖不良

(2)侵蚀:主要发生在密集排列的细金属线阵列周围。在高图形密度区域,抛光垫的局部压力分布更为集中,加上化学作用的协同效应,导致介质层被过度去除而显著减薄。侵蚀会改变层间介质的有效厚度,影响寄生电容,进而干扰电路的电学性能,同时增大表面台阶高度,使后续CMP难以实现全局平坦化。

从上述缺陷发生机制来看,IC抛光并非单一工序,而是需要针对芯片不同功能层的特性,开展针对性的抛光处理。以下以浅沟隔离槽(STI)抛光、氧化物层间介质抛光与金属抛光等核心的环节举例:

(1)浅沟隔离槽(STI)抛光:

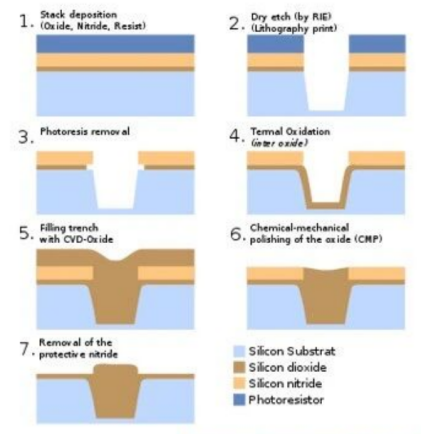

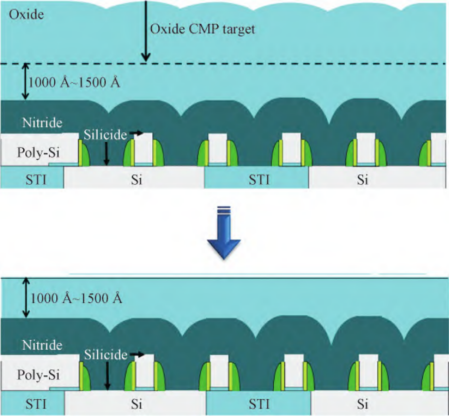

STI主要用于分隔相邻晶体管,具体工艺为:首先在硅衬底上依次沉积氧化硅层和氮化硅层,前者起到初步电气隔离作用,后者作为阻挡层,用于保护硅衬底在后续热氧化与刻蚀过程中不受损伤。之后再刻蚀出浅沟槽并填充绝缘氧化物(通常为SiO₂),最终通过CMP去除沟槽外多余的氧化物,仅保留沟槽内的隔离层,使氧化物表面与氮化硅阻挡层表面共面。在该过程中,CMP抛光核心难点在于选择性控制,要求在完全去除沟槽外氧化物的同时,尽可能减少沟槽内氧化物的过度去除,以及抑制Si₃N₄阻挡层去除,避免产生“沟槽氧化物蝶形凹陷”。

(2)层间介质(ILD)抛光:在多层金属互连结构中,每一层金属布线完成后,需要在其上方沉积一层绝缘介质(即层间介质,通常为SiO₂或低k材料),将上下两层金属电气隔离。该阶段的抛光主要用于去除层间介质沉积过程中产生的表面凹凸不平,为后续金属互连层的沉积提供平坦的基底。在这一过程中,需要确保抛光后残留的介质层厚度足够实现金属层间的电气隔离,同时避免过度抛光损伤下层结构。

(3)Low-k 介质材料抛光:为减小互连延迟,降低介质材料介电常数成为芯片工艺的核心发展方向,但主流 Low-k 介质材料为多孔材料、改性二氧化硅或聚合物材料,机械强度低,化学稳定性差,极易在CMP过程中发生损伤。因此,Low-k介质抛光需采用低压力、低损伤的工艺方案,严格控制抛光速率与化学作用强度,、保护材料结构完整性,避免k值偏移与缺陷产生。

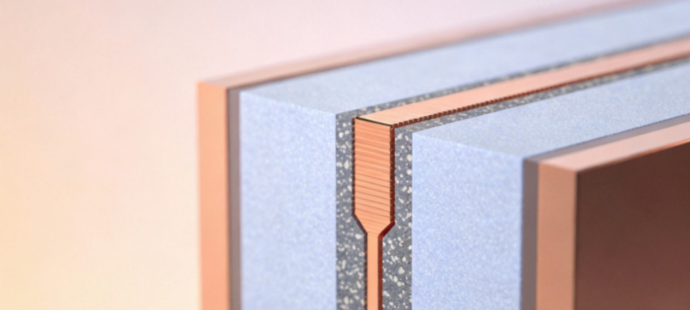

(4) 金属互连抛光:主要用于去除金属沉积过程中多余的金属材料(如铜、钨、钴、钌等),形成精准的金属互连线路与通孔,实现芯片内部不同晶体管的电气连接,其抛光需根据不同金属材料的特性,实现金属与介质层的选择性抛光,确保金属线路的尺寸精度与表面平整度。

IC抛光中“纳米级平衡”的本质,是在化学腐蚀速率与机械去除速率之间找到精确匹配点,使不同材料的去除速率既满足效率要求,又能抑制蝶形下陷、侵蚀等缺陷,而这需要抛光液、抛光垫与工艺控制之间实现系统协同。

1、高选择比抛光液设计

抛光液作为CMP工艺中化学作用的核心载体,包括氧化剂、络合剂、缓蚀剂、磨料等,其配方设计直接决定多介质材料的腐蚀速率与去除平衡,是实现纳米级共面的基础。因此,其配置核心在于精确调控不同材料的去除速率选择比,以便能更有效地去除目标材料(如铜),同时较少地去除非目标材料(如介质层),有助于减少碟形下陷、侵蚀等缺陷,提高表面平整度和工艺良率。

比如,在STI-CMP和ILD-CMP抛光中,抛光液主要采用采用粒径为10-100nm的CeO₂作为核心磨料,体系为中性至弱碱性,由于氧化铈具有高表面活性,能与硅氧化物(SiO₂)形成临时化学键,实现“化学吸附+机械去除”的协同抛光机制,最终使得SiO₂与Si₃N₄的去除速率比达30-100:1,确保沟槽边缘的精准停刻。而针对Low-k介质的抛光,其机械应力必须严格控制,通常采用30nm 以下的软质磨料(如有机硅球),并添加 PEG 等润滑剂降低摩擦系数,避免材料出现裂纹或分层,避免k值升高,同时引入高效抑制剂减少材料损伤。

2、抛光垫的设计

抛光垫承担着支撑晶圆、输送抛光液、传递压力、去除废料等多重功能。而影响抛光效率和精度的主要因素有硬度、多孔结构、沟槽等。

·多孔结构设计:通常抛光垫表面设计为多孔蜂窝状结构,孔隙率控制在20%~40%,既能留存足够的抛光液,又能及时排出碎屑,避免碎屑残留导致表面缺陷。

·硬度控制:抛光垫的硬度需根据不同抛光环节、不同材料进行适配。比如金属抛光(如钨)需选用高硬度抛光垫,提升机械研磨效率;介质层抛光(如氧化硅)则需选用中低硬度抛光垫,减少表面损伤;Low-k介质抛光则需选用超软垫,降低机械应力,避免材料塌陷、开裂。

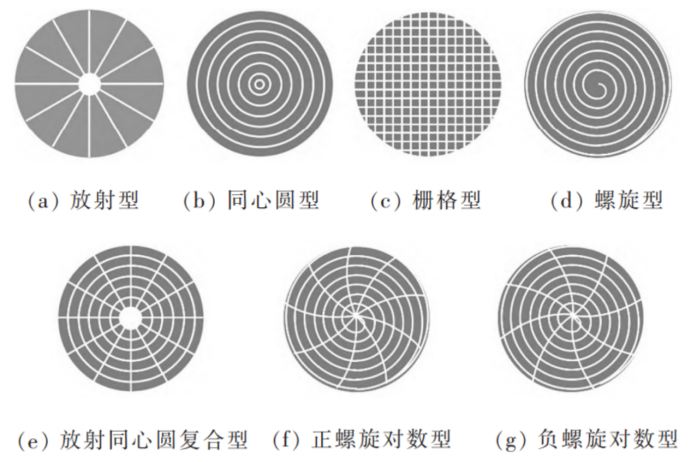

·沟槽设计:抛光垫表面的径向或螺旋沟槽有助于抛光液的均匀分布和快速更新,同时优化废料排出效率,目前常见的沟槽形式有放射型、网格型、圆环型以及螺旋对数型等,通常将多种沟槽结构结合设计成效果普遍比单一型更优。

常见抛光垫沟槽结构

此外,抛光垫在使用过程中会因磨损、碎屑堵塞导致表面状态变化,需搭配抛光垫修整器,通过金刚石颗粒对抛光垫表面进行微量切削,以恢复其粗糙度与孔隙结构,确保每片晶圆的抛光一致性。

3、工艺控制

工艺控制的核心目标是实现化学作用与机械作用的动态匹配,以及多介质材料去除速率的实时调控。针对IC抛光的复杂场景,可引入多区压力调控、原位终点检测 、自适应控制等机制。

·工艺参数优化:现代12英寸CMP装备普遍采用多区压力调控技术,抛光头被划分为多个同心圆环分区,每个分区的压力可独立调节,以补偿芯片边缘效应和薄膜厚度不均匀性。此外,也可集成智能化控制系统,根据实时监测数据动态调整抛光参数(如压力、转速、流量等),实现自适应优化,提高加工一致性和良率。

·原位终点检测:由于IC抛光需精准控制不同材料的去除厚度,仅依靠时间控制无法满足纳米级精度要求,需采用高精度实时监测系统,通过光学干涉、电涡流效应或电机电流分析法,实时监测抛光过程中芯片表面的厚度变化与材质信号,当检测到目标材料(如阻挡层Ta/TaN)的信号时,立即停止抛光,有效避免碟形坑、侵蚀等缺陷的产生。

小结

相比于单一材料的晶圆衬底抛光,IC集成电路抛光面临多介质、多结构、高深宽比等复杂场景,蝶形下陷与侵蚀两类典型缺陷成为制约良率的关键瓶颈。CMP 的本质是化学腐蚀与机械研磨的精密协同,而要实现纳米级平坦化,核心在于抛光液配方、抛光垫结构与智能化工艺控制三者的协同。只有牢牢掌握 CMP 全链条核心技术,才能打通先进制程制造的关键堵点,为高性能芯片的稳定量产提供坚实支撑。

粉体圈Corange整理