4月27日,全球先进陶瓷领导者京瓷集团(Kyocera)宣布,随着AI数据中心不断向大型化发展的xPU、交换ASIC等尖端半导体封装升级,公司开发了一种独有的多层陶瓷基板,可实现高密度布线,还能降低封装时的翘曲度。京瓷计划在5月美国举行的半导体封装国际会议(ECTC2026)上正式展出。

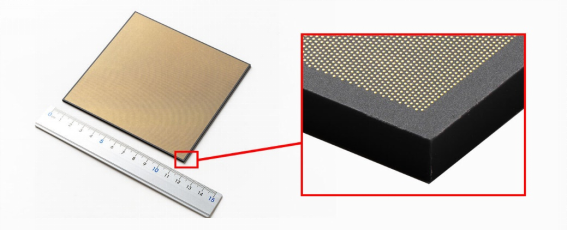

京瓷开发的新型陶瓷基板焊盘(Pad)直径:75µm、间距:200µm

编者注:

以上,xPU泛指各种GPU(图形处理器)、TPU(张量处理器)、NPU(神经网络处理器)、DPU/IPU(数据处理/基础设施处理器)等,负责计算、加速和数据处理的各种专用处理器;交换ASIC是数据中心网络交换机的核心芯片,它负责在 GPU 服务器、计算节点之间高速转发数据包;焊盘即基板表面焊接芯片的金属触点。

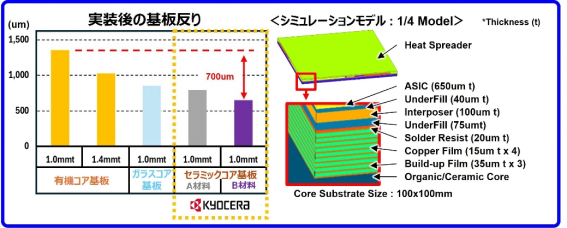

面对AI数据中心的高功耗,大芯片以及芯片上的凸点间距越来越密的趋势,原有机封装基板与芯片热膨胀系数不匹配导致的整体弯曲会导致焊点断裂、接触不良,并且也难以做出细线宽/线距。京瓷开发这种高刚性、低热膨胀的陶瓷材料作为基板核心层,即作为面向下一代超大尺寸 AI 芯片封装(如超过 100×100mm)的解决方案。

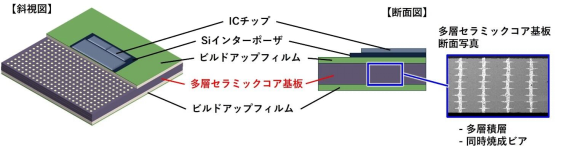

京瓷表示,随着生成AI和大规模语言模型(LLM)的普及,全球范围内数据中心的建设与扩展正在加速,基于2.5D封装的封装基板大型化和高密度布线正在加速,有机基板已无法满足上述趋势要求。在上述背景下,京瓷对陶瓷基板封装项目进行开发。

2.5D封装对比(有机、玻璃、多层陶瓷)示意图

如上所示,陶瓷基板可减少翘曲和利于减薄,并且在垂直连通的通孔加工是生坯加工工艺,因此加工精度更高。京瓷表示,公司还能够根据客户的设备规格和实施条件,进行热应力、电仿真以及考虑部件安装过程的电路板翘曲仿真等应对措施,并且基于这些测试结果给出层压陶瓷核心板的定制设计建议。

编译整理 YUXI